PlasticArm: Get Your Next CPU, Made Without Silicon

by Dr. Ian Cutress on July 22, 2021 8:01 AM EST

Known for its core design IP that ends up in everything from IoT to smartphones to servers, Arm is now presenting that it has enabled one of its key microcontrollers in a new form factor: rather than using silicon as a base, the company has enabled a processor core in plastic. The technology has been in the works for almost a decade, but Arm has been waiting on the fabrication methods to create a fully working core. Now the company has something working in a tangible medium and the research has been published in Nature.

Creating a Plastic CPU

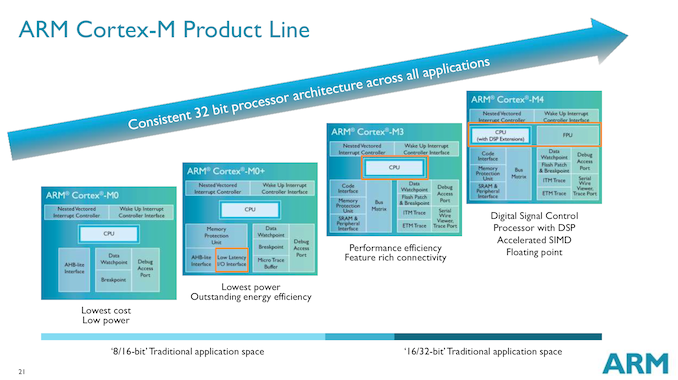

'Plastic' or flexible electronics have been with us for a long while, and usually involve large yet simple designs for electronics flow, or basic 8-bit adders, all the way up to displays. What we're seeing now is something a little different - the key news as published today is that Arm, in association with PragmatIC, has produced a fully functional non-silicon version of one of Arm’s most popular microcontrollers, the M0.

This M0 core sits right at the bottom of Arm’s core product stack, however the minimalist design is a popular one for silicon processors due to its low die area and power requirements for simple microcontroller tasks. So while it won’t be powering your next big device any time soon, lots of integrated electronics that you own will likely already be relying on M0 cores for fundamental control tasks.

PlasticArm, as it is now called, recreates the M0 core in a flexible plastic medium. This is important in two factors – first, the ability to enable processors or microcontrollers in something other than silicon will allow some amount of programmability in packaging, clothing, medical bandages, and others. Paired with a particle sensor, for example, it might allow for food packaging to determine when what is inside is no longer fit for human consumption due to spoilage or contamination. The second factor is cost, with flexible processing at scale being orders of magnitude cheaper than equivalent silicon designs. To Arm’s credit, the new M0 design here is reported to be 12x more powerful than current state-of-the-art plastic compute designs.

Details on the Plastic M0

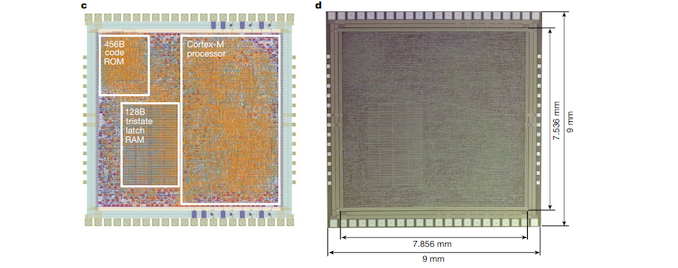

In Arm’s press release, the company states that the Plastic M0 design has 128 bytes of RAM and 456 bytes of ROM, while also supporting a 32-bit Arm microarchitecture.

Inside the research paper published at Nature, we get fine-grained details.

The processor is built with a polyimide substrate and is formed through thin-film metal-oxide transistors, such as IGZO TFTs. This means that this is still technically a photolithography process, using spin-coating and photoresist techniques, ending up with the processor having 13 material layers and 4 routable metal layers. However as TFT designs have been widespread since the use of IGZO displays, the cost of production is still quite low.

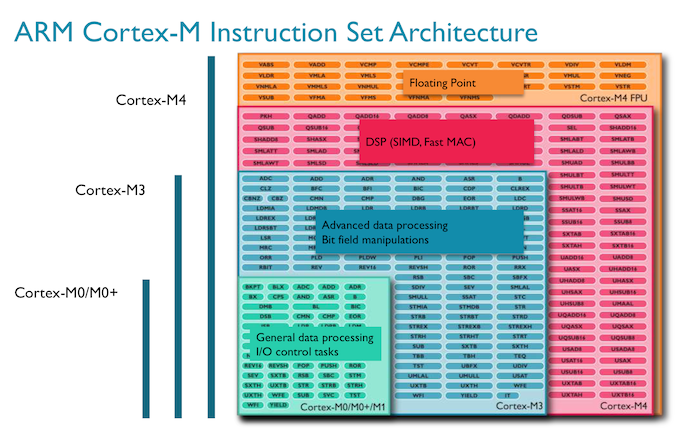

The core supports the ARMv6-M architecture, with a 16-bit Thumb ISA combined with a sub-set of 32-bit Thumb. As with the regular M0, data and address widths are 32-bit, the in-order design is a 2-stage pipeline, and the core supports 86 instructions. The main difference to a silicon M0 core is that the register file, rather than being inside the CPU, is mapped to the 128-byte bank of DRAM. This is because the TFT design is better supported through a memory mapping technique. Despite this, the Plastic M0 core is binary compatible with all other Cortex M0 cores.

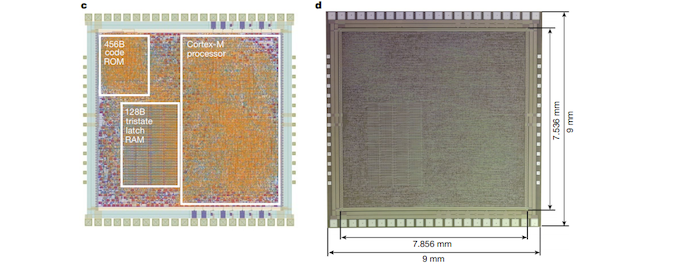

A typical die size for a silicon Cortex M0 using TSMC’s 90nm process is 0.04 mm2, whereas PlasticArm is using an equivalent 800nm TFT process and the core size is 59.2 square millimeters (7.536 mm x 7.856 mm). This makes the Plastic M0 core about 1500x the size of a standard IoT implementation. The other big difference is in frequency – the research paper states that the Plastic M0 runs at around 20-29 kilohertz with a 3V input; an M0 on a 180nm Ultra-Low Leakage process optimized for power rather than frequency, in Arms own design documents, can run at 50 MHz. That’s a 1600-2500x difference in frequency.

| PlasticArm: the Plastic M0 | |

| Process Node | FlexIC 800nm n-type IGZO TFT 200nm polyimide wafer |

| Die Size | 59.2 mm2 (core only) (7.536 mm x 7.856 mm) |

| Thickness | under 30 micron |

| ISA | ARMv6-M 16-bit Thumb + subset of 32-bit |

| Frequency | 20-29 kilohertz |

| Power | 21 milliWatts |

| Pin Count | 28 pins |

| Material Layers | 13 layers |

| Routable Metal Layers | 4 layers |

| Devices | 56340 39157 n-type TFT + 17183 resistors |

The Plastic M0 design uses 56340 devices, which is a mix of 39157 thin-film n-type transistors and 17183 resistors. Because the goal of this design was to not have any physically added resistors, the paper documents that implementing resistors at a TFT level within the layers involves using photolithography materials with higher resistance to enable a smaller size. Overall the paper predicts an equivalent silicon design of 18334 NAND2 gates. Overall power for the Plastic M0 core at 29 kHz is listed at 21 mW, 99% of which is static power (45% core, 33% memory, 22% IO). The 28 pins on the processor allow for clock signal generation, reset, GPIO, power, and debug.

Research Scope

In its press release, Arm states that one of the main barriers to production was down to technology and fabrication limitations – the project started in 2013 and even a prototype circuit was shown at Arm TechCon in 2015 using ring oscillators, counters, and shift register arrays. However a number of key questions were still left unsolved, mostly down to cell libraries for all the different components of a modern processor, along with tool flow and production. Over time Arm’s partner PragmatIC, through other projects it was working on, was able to build a range of cell libraries congruent with what was needed for an M0 processor. The first PlasticArm manufacture and validation was reportedly performed in October 2020.

Arm’s research points to cell library production being a key to unlocking further designs in the future. As microcontrollers and processors get more complex more elements (and different types) are needed to create an end-to-end useable product. Going beyond M0 thus requires research into enabling individual libraries in a TFT design. Beyond this, the research paper also states that low-power libraries are needed to enable scale. Because most of the power consumption on Plastic M0 is static power, driving that down through design and manufacturing is going to be a direction of research. There is also the angle of manufacturing – this was all done on a photolithography process using 200nm polyimide wafers using deposition techniques. An ultimate goal of plastic processors is that size is less of a limitation, and they can be ‘printed’ using conventional ink techniques. We’re not there yet, but this is certainly a step in that direction.

So while we can’t buy an Apple M1 built-in plastic just yet, there seems to be plenty of future potential in the technology.

Related Reading

- Arm Announces Mobile Armv9 CPU Microarchitectures: Cortex-X2, Cortex-A710 & Cortex-A510

- Arm Announces New Mali-G710, G610, G510 & G310 Mobile GPU Families

- Arm Announces Neoverse V1, N2 Platforms & CPUs, CMN-700 Mesh: More Performance, More Cores, More Flexibility

- Arm Announces Armv9 Architecture: SVE2, Security, and the Next Decade

- The Ampere Altra Review: 2x 80 Cores Arm Server Performance Monster

34 Comments

View All Comments

Oxford Guy - Sunday, July 25, 2021 - link

The Atari 2600 had 128 bytes of RAM and a much higher-clock but also simpler CPU (fewer transistors).The Fairchild Video Entertainment System had 64 bytes of scratchpad RAM but also a faster clock than this, despite the fact that the CPU wasn’t on a single die.

The Fairchild, to my knowledge, didn’t have a graphics accelerator chip — relying instead on the CPU to work with its whopping 4 colors and low resolution.

The Atari, which was hardware-upgraded after the release of the VES (in order to be significantly better) had a sound chip and some sort of odd graphics chip that drew everything line by line from a point as I hazily recall. It enabled a large color palette and rainbow effects but also had big drawbacks.

So, would this be fast enough to run a Fairchild VES game, one that didn’t come with on-cart RAM (as Maze and Chess did)? Or, is the 29 KHz speed just too slow, even with a much more powerful CPU design? I assume it can handle VES games but wonder more about 2600 games, let’s say if this chip were given the TIA sound chip and whatever the GPU was.

(Interestingly, the Intellivision is odd because it shipping with a 16-bit CPU — internally, the bus was cut to 8 bits — and ran in the KHz, not MHz, range. I think the RAM was also very slow due to how it was implemented but it’s hard to remember the details.)

mode_13h - Sunday, July 25, 2021 - link

Thanks for the specs. I didn't know about anything quite that far back.Oxford Guy - Monday, July 26, 2021 - link

The Maze game shipped with 1K of SRAM and Chess had 6K, which was massive at the time.Fairchild would have been better off to have given the base unit more RAM rather than ‘waste’ chips in Maze cartridges. That 1K was needed for the AI of the ‘cat’ in the ‘Cat and Mouse’ version of the Maze game.

Oxford Guy - Monday, July 26, 2021 - link

It’s hilarious to think that this CPU has less RAM (much much less) than the Maze cartridge for the 1976 Fairchild console.