Intel Executive Posts Thunderbolt 5 Photo then Deletes It: 80 Gbps and PAM-3

by Dr. Ian Cutress on August 1, 2021 1:29 PM EST

An executive visiting various research divisions across the globe isn’t necessarily new, but with a focus on social media driving named individuals at each company to keep their followers sitting on the edge of their seats means that we get a lot more insights into how these companies operate. The downside of posting to social media is when certain images exposing unreleased information are not vetted by PR or legal, and we get a glimpse into the next generation of technology. That is what happened today.

Day 1 with the @intel Israel team in the books. Great views…incredible opp to see @GetThunderbolt innovation …a validation lab tour and time with the team…can’t wait to see what tomorrow brings! pic.twitter.com/GKOddA6TNi

— Gregory M Bryant (@gregorymbryant) August 1, 2021

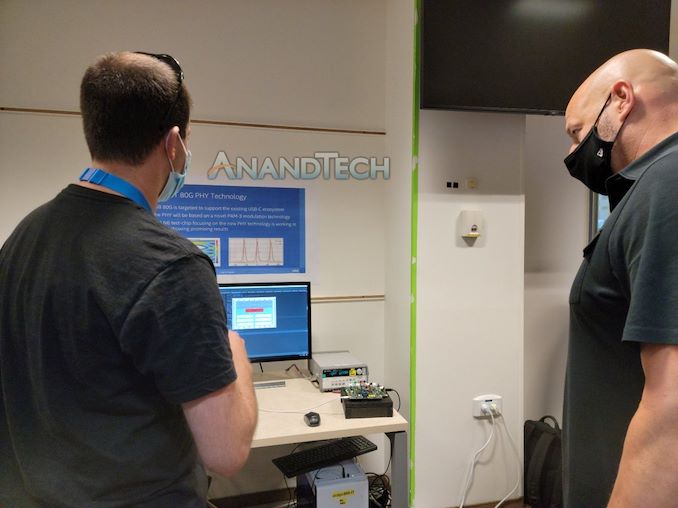

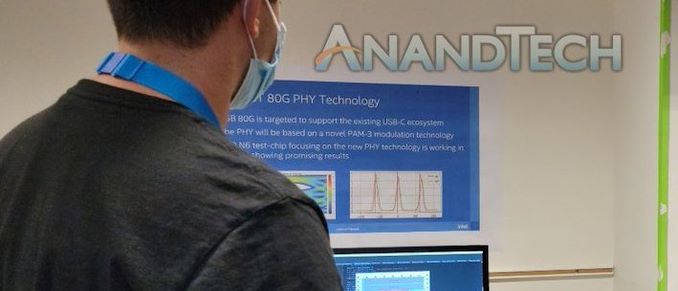

EVP and GM of Intel’s Client Computing Group, Gregory Bryant, is this week spending some time at Intel’s Israel R&D facilities in his first overseas Intel trip in of 2021. An early post on Sunday morning, showcasing Bryant’s trip to the gym to overcome jetlag, was followed by another later in the day with Bryant being shown the offices and the research. The post contained four photos, but was rapidly deleted and replaced by a photo with three (in the tweet above). The photo removed showcases some new information about next-generation Thunderbolt technology.

In this image we can see a poster on the wall showcasing ‘80G PHY Technology’, which means that Intel is working on a physical layer (PHY) for 80 Gbps connections. Off the bat this is double the bandwidth of Thunderbolt 4, which runs at 40 Gbps.

The second line confirms that this is ‘USB 80G is targeted to support the existing USB-C ecosystem’, which follows along that Intel is aiming to maintain the USB-C connector but double the effective bandwidth.

The third line is actually where it gets technically interesting. ‘The PHY will be based on novel PAM-3 modulation technology’. This is talking about how the 0 and 1s are transmitted – traditionally we talk about NRZ encoding, which just allows for a 0 or a 1 to be transmitted, or a single bit. The natural progression is a scheme allowing two bits to be transferred, and this is called PAM-4 (Pulse Amplitude Modulation), with the 4 being the demarcation for how many different variants two bits could be seen (either as 00, 01, 10, or 11). PAM-4, at the same frequency, thus has 2x the bandwidth of an NRZ connection.

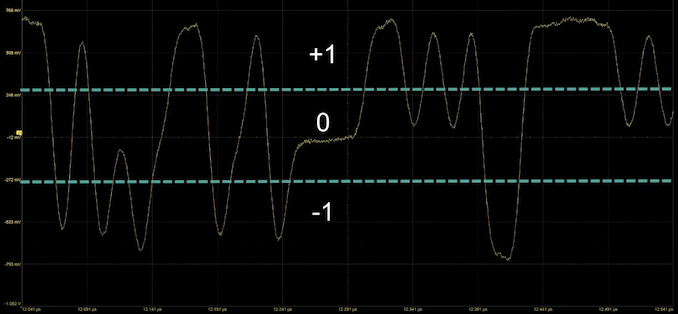

So what on earth in PAM-3?

From Teledyne LeCroy on YouTube

PAM-3 is a technology where the data line can carry either a -1, a 0, or a +1. What the system does is actually combine two PAM-3 transmits into a 3-bit data signal, such as 000 is an -1 followed by a -1. This gets complex, so here is a table:

| PAM-3 Encoding | ||

| AnandTech | Transmit 1 |

Transmit 2 |

| 000 | -1 | -1 |

| 001 | -1 | 0 |

| 010 | -1 | 1 |

| 011 | 0 | -1 |

| 100 | 0 | 1 |

| 101 | 1 | -1 |

| 110 | 1 | 0 |

| 111 | 1 | 1 |

| Unused | 0 | 0 |

When we compare NRZ to PAM-3 and PAM-4, we can see the rate of data transfer for PAM-3 is in the middle of NRZ and PAM-4. The reason why PAM-3 is being used in this case is to achieve that higher bandwidth without the extra limitations that PAM-4 requires to be enabled.

| NRZ vs PAM-3 vs PAM4 | |||

| AnandTech | Bits | Cycles | Bits Per Cycle |

| NRZ | 1 | 1 | 1 |

| PAM-3 | 3 | 2 | 1.5 |

| PAM-4 | 2 | 1 | 2 |

PAM-3 has similar limitations to NRZ.

The final line on this image is ‘[something] N6 test-chip focusing on the new PHY technology is working in [the lab and] showing promising results’. That first word I thought was TSMC, but it has to be about the same width as the ‘The’ on the line above. So it doesn’t look like I’m right there, but N6 is a TSMC node.

Intel’s goal with Thunderbolt is going to be both driving bandwidth, power, and utility, but also right now it seems keeping it to the USB-C standard is going to be a vital part of keeping the technology useful for users who can fall back on standard USB-C connections. Right now Intel’s TB4 is a superset that includes USB4, so we might see another situation where TB5 is ready to be a superset of USB5 as well, however it seems that USB standards are slower to roll out than TB standards right now.

Special thanks to David Schor from WikiChip for the tipoff.

Related Reading

- Intel's CES 2021 Press Event: The Future of Intel (A Live Blog, 1pm PT)

- Intel Launches 11th Gen Core Tiger Lake: Up to 4.8 GHz at 50 W, 2x GPU with Xe, New Branding

- Intel Thunderbolt 4 Update: Controllers and Tiger Lake in 2020

- Intel’s 11th Gen Core Tiger Lake SoC Detailed: SuperFin, Willow Cove and Xe-LP

- DisplayPort Alt Mode 2.0 Spec Released: Defining Alt Mode for USB4

- Cypress Announces USB 3.2 & USB4-Ready Controllers: EZ-PD CCG6DF & CCG6SF

- USB 3.2 Gen 2x2 State of the Ecosystem Review: Where Does 20Gbps USB Stand in 2020?

82 Comments

View All Comments

lightningz71 - Sunday, August 1, 2021 - link

It's all about signal states. If you can combine "amplitude modulation" with "frequency modulation" and manage to define multiple "zones" that represent the combination of, let's say high amplitude and fast modulation, high amplitude and slow modulation, low amplitude and fast modulation, and finally low amplitude and slow modulation, you have four distinct "zones" per clock to carry information, giving you two total bits per cycle. What you then need is circuits that can detect what zone the signal is at each given clock cycle, and can do it fast enough to run at a high signaling rate.You can then refine this to have more states per modulation and amplitude, similar to the way you can have many different voltages in a NAND cell such as in a QLC cell. You can have four detectable frequencies and four detectable areas of amplitude to give 16 different possible combinations for four bits of data per clock cycle.

However, with the more and tighter ranges, the more chances of data errors there are. You can solve that by including parity bits, CEC checks, and, using complex encoding with rotating bit ranges (look up how the physical layer of Ethernet works).

This is ALL a GROSS oversimplification of how it works, but it gives you the fundamental idea.

FunBunny2 - Monday, August 2, 2021 - link

"This is ALL a GROSS oversimplification"useful, nevertheless. thx.

minde - Sunday, August 1, 2021 - link

thunderbolt 5 . With pcie4? its good for 8k 60p video. on intel 7nm or 7nm+ 2023-2025?Ian Cutress - Sunday, August 1, 2021 - link

You mean Intel 4 and Intel 3minde - Sunday, August 1, 2021 - link

yes. on 7nm on Xe GPU up to 192 EUsDigitalFreak - Monday, August 2, 2021 - link

It's sad to see that you've so readily bought into that Intel marketing BS.A5 - Monday, August 2, 2021 - link

All process node names have been marketing BS for at least a decade. If you think there are meaningful feature size differences between (for ex) Samsung 8LP 7HFP 6LPP or whatever, you'd be wrong.dotjaz - Monday, August 2, 2021 - link

It's sad you bought into mere names in rhe first place.mode_13h - Tuesday, August 3, 2021 - link

It's sad you bought into buying into things!; )

mode_13h - Tuesday, August 3, 2021 - link

Why do you think that? He specifically lobbied them for it!The fact is that we really don't have good data on the real feature size or density of their latest 10 nm iterations. So, there's nothing else you *can* call it that's necessarily accurate.