Intel at ISSCC 2015: Reaping the Benefits of 14nm and Going Beyond 10nm

by Ian Cutress on February 22, 2015 3:00 PM EST

As part of the International Solid-State Circuits Conference every year, Intel brings forward a number of presentations regarding its internal research. The theme this year at ISSCC is ‘Silicon Systems – Small Chips for Big Data’, and Intel previewed a number of their presentations with the media and analysts last week before the conference. Hot topics being talked about include developments for 14nm features that could potentially be ported to real world devices, technological developments at 22nm using Tri-Gate CMOS for adaptive, autonomous and resilient systems and also a few quick words regarding 10nm and beyond.

Taking Moore’s Law Beyond 10nm

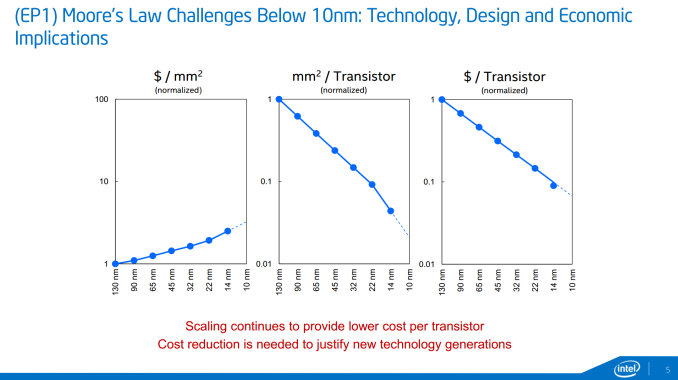

Part of ISSCC will be a round table with representatives from Intel, Qualcomm, a couple of industry companies and university researches discussing how 10nm will attack Moore’s Law and how it can be extended below to 7nm. The graphs shown at IDF 2014 make their presence again, showing cost per square mm and cost per transistor, courtesy of Mark Bohr (Intel Senior Fellow, Logic Technology Development):

The fact that 14nm resulted in a better-than-the-trend drop in cost per transistor was explained as some internal smart reworking, making sure that certain areas of the dies require different masking and by optimizing the masking process, the cost can be reduced rather than relying on fewer general masks (but it is still a balance).

It was explained that while 10nm will have more masking steps than 14nm, and the delays that bogged down 14nm coming late to market will not be present at 10nm – or at least reduced. We were told that Intel has learned that the increase in development complexity of 14nm required more internal testing stages and masking implementations was a major reason for the delay, as well as requiring sufficient yields to go ahead with the launch. As a result, Intel is improving the efficiency testing at each stage and expediting the transfer of wafers with their testing protocols in order to avoid delays. Intel tells us that that their 10nm pilot lines are operating 50% faster than 14nm was as a result of these adjustments. So while the additional masking steps at 10nm which ultimately increases fixed costs, Intel is still quoting that their methods results in a reducing in terms of cost per transistor without needing a completely new patterning process. EUV lithography was discussed, but Intel seems to be hoping to avoid it until it is absolutely necessary, as EUV development so far has been slower to progress than expected.

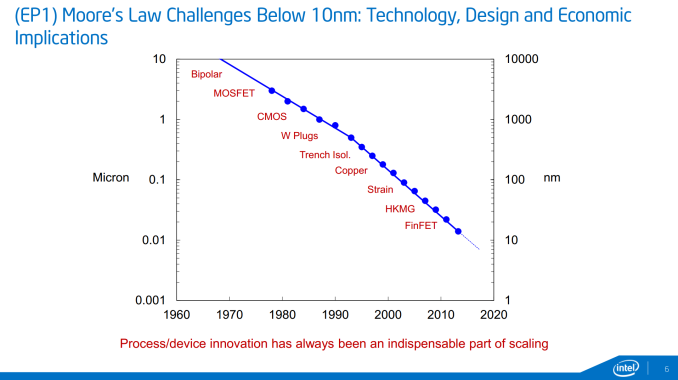

10 nm will come with innovation, and getting down to 7 nm will require new materials and processes which Intel wants to promote as a progressive integration between process development and the product design teams. New materials and device structures are key elements on that list, and while III-V materials were discussed in the ISSCC preview, no exact details were given.

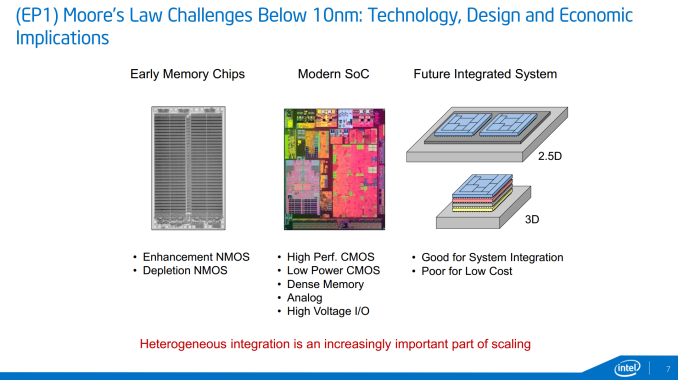

Along with addressing the general challenges in getting down to 7nm, Intel's research group is also looking to address future integrated systems, specifically 2.5D (separate dies on an interposer) and 3D (stacked dies). While 2.5D and 3D are not direct replacements for smaller manufacturing nodes - they just allow you to lay down more transistors at a higher cost - they are being examined as potential solutions for containing power consumption in certian situations (2.5D) or in building better size-limited integrated topologies (3D). Specifically, Intel is looking at scenarios where logic blocks using different fabrication methods are laid out in their own layers and stacked, rather than implemented on a single layer of a single die (think memory, digital logic, and analog communications on a single chip).

These kinds of configuration may appear in smartphones, tablets, or other devices that use highly-integrated chips where multiple types of fabrication would be necessary, and where manufacturers can charge the premium price necessary to cover the additional costs. We have discussed in the past how 2.5D and 3D configurations can improve performance, especially when it comes to memory density and graphics bandwidth, however the price increase (according to Intel) will result in that premium, even at high volume.

Reaping the Benefits of 14nm

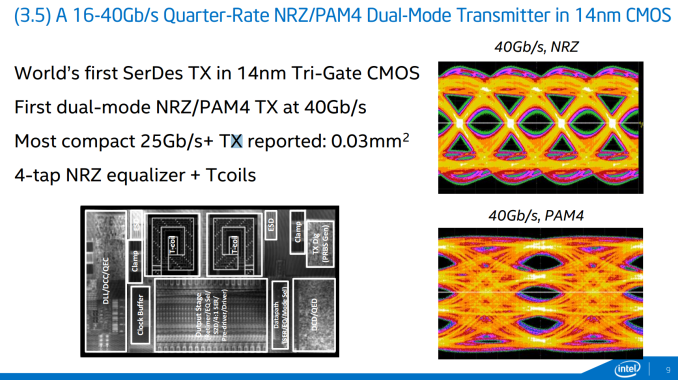

Intel is highlighting a trio of papers at ISSCC regarding 14nm. One of the areas ripe for exploitation at 14nm is data transfer, especially transmitters. To that extent, Intel is showing a 14nm Tri-Gate CMOS serializer/deserializer transmitter capable of 16-40 Gbps, using both the NRZ (non-return zero) and PAM4 (Pulse-Amplitude Modulation with 4 levels) modes within a 0.03 millimeter squared die area.

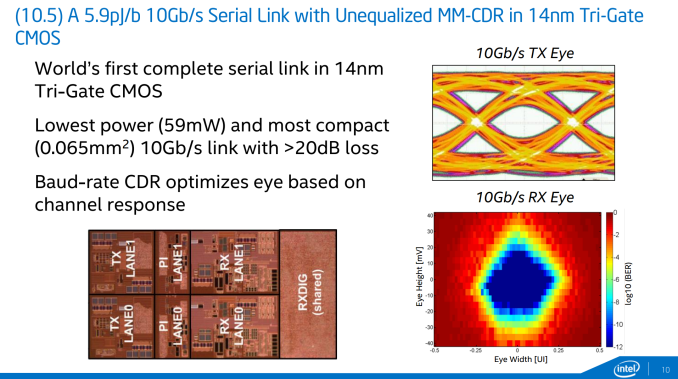

Also on data transfer is a paper regarding the lowest power 10Gb/s serial link and the first complete serial link using 14nm Tri-Gate CMOS. Intel has working silicon at 14nm showing a 59mW power consumption within 0.065 millimeters squared die area that configures the committed data rate to provide the cleanest data response.

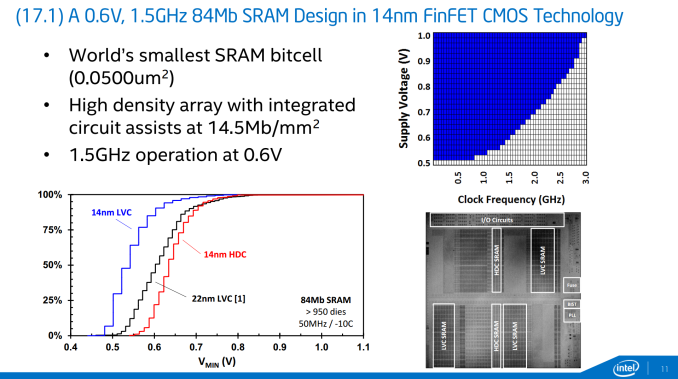

Perhaps the most exciting 14nm development is in the form of memory, with Intel describing in-house 84Mb SRAM design that uses the world’s smallest bitcell (0.050 micron squared). At 14nm it represents a doubling of the density at 14.5 Mb per square millimeter, but also provides substantially lower minimum voltage for a given frequency compared to the previous 22nm process. As shown in the graph in the slide, 0.6V is good for 1.5 GHz, but it can scale up to 3 GHz. It is also worth noting that the 14nm yield gradient is more conducive to lower voltage operation compared to the 22nm process. While it seems odd to promote an 84Mb (10.5 MB) design, Intel discussed that it can be scaled up over 100 Mb or more, making it a better solution for embedded devices rather than something like Crystal Well on desktop.

Still Developing on 22nm

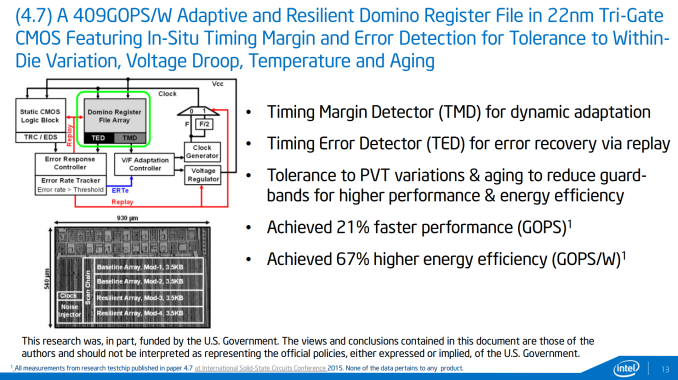

While 14nm is great for density, lower voltage and lower power, other features on die are often produced at a looser resolution in order to ensure compatibility but it also offers a great research platform for testing new on-die features to be scaled down at a later date. To this extent, Intel Labs is also presenting a couple of papers about in-house test chips for new features.

The first test chip concerns data retention within register files. Depending on the external circumstances such as temperature and age, this adaptive and resilient domino register file testchip is designed to realign timing margins and detect errors as they occur and adjust the behavior in order to compensate. The logic that Intel is presenting is designed to also cater for die variation and voltage droop, making it more of a universal solution. On a higher level it sounds like the situation when NAND flash gets old and the onboard controller has to compensate for the voltage level margins.

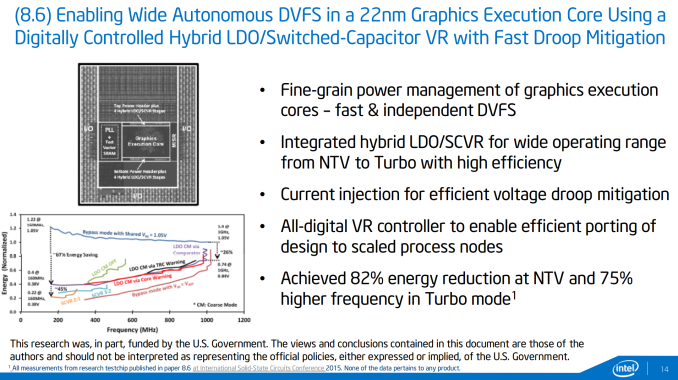

The second test-chip being described brings the situation down to Intel’s execution units in its graphics and dealing with fast, autonomous and independent dynamic voltage scaling. The use of a combined low-dropout regulator (LDO) for low voltages, such as at idle, and a switched capacitor voltage regulator (SCVR) for high voltages allow the appropriate current injection to deal with voltage droop as well as resulting in a large energy reduction. When applied, this should allow for either a power drop at the same frequency, or a higher frequency at the same voltage. Currently the numbers provided by Intel are all on internal silicon rather than anything in the wild, and will be examined at smaller nodes in due course.

Intel at ISSCC

ISSCC always throws out some interesting information about what is actually going on under the hood with the silicon we use almost every day, as we tend to think about it as a black box that slowly gets better over time. In reality, new features are fully researched and documented in order to be included in the next model, as well as trying to keep a balance of power usage and efficiency. On the CPU architecture side of the equation, we reported that Broadwell features needed to show a 2% performance or efficiency improvement for every 1% increase in power, making that advancement steeper than the 1:1 previously required. For all intents and purposes this means that if the same strategy is applied to 10nm and beyond, we are in for a very interesting time. It was interesting to hear about Intel speeding up on 10nm to avoid the delays occurred at 14nm, as well as thoughts regarding future technologies.

The papers Intel is presenting should be available via the ISSCC website as the presentations take place, along with a few others that pique our interest. This should get us ready for some interesting developments come Intel's Developer Forum later in the year.

55 Comments

View All Comments

mkozakewich - Monday, February 23, 2015 - link

Your entire argument is that you're a gamer and they don't make graphicsless chips at a lower price for you.I personally like the longer battery life.

voicequal - Sunday, February 22, 2015 - link

I'd guess you would't be as satisfied with 45nm on your smart phone.TeXWiller - Sunday, February 22, 2015 - link

Rather than anything related to Flash, the domino register file experiment sound like chip-by-chip longevity and reliability optimization for embedded systems. The partial government funding should support that viewpoint.Frenetic Pony - Sunday, February 22, 2015 - link

Eugh, 3-5 groups and EUV. 3-5 stuff is poisonous (literally, you have to deal with environmental issues and etc.) as well as being more expensive than silicon. EUV has a huge amount of problems, from requiring multiple patterning to increasing amounts of manufacturing isolation being needed. Intel seems bent on running itself into the dead end of Moore's law while ignoring the obvious advantages of materials other than silicon and the established alternatives.Graphene can be produced in large quantities, isolated from the environment, reliably given a controllable bandgap, and with the charge carrier mobility and severely low leakage make any advancement in Moore's law even into single molecules obsolete and useless in comparison. And while there are still challenges it's a lot more exciting to see clockspeeds potentially scaling to hundreds of gigahertz and above, with optical data transfer (easily doable into transitions with graphene) to feed data from memory there's little reason we can't scale to that.

Even if graphene somehow proves too onerous, though it hasn't so far, there's other alternatives like black phosphorous and other 2d carbon allotropes to choose from that could produce similar to better results. Who needs overly clever engineering design and plowing billions into ever higher resolution lithography when you can just run at a high enough clockspeed (And low enough voltage) to make a single core with a new material outpace hundreds of silicon based cores?

Michael Bay - Sunday, February 22, 2015 - link

What makes you think intel is not researching their options in this field also?They sat on their 3d transistor technology for years if not a decade, we may well see something not on conventional silicon from them, but only when they drain it completely as a tecnology.

stadisticado - Sunday, February 22, 2015 - link

As Mr. Bay says, you're presuming Intel (or the other foundries) aren't investigating these things. Graphene is indeed interesting but logic die built on that process don't meet current consumer needs. Additionally, I haven't seen any news relating to wafer processing suppliers (ASML, Hitachi, TEL, etc.) getting behind that tech. Even if an Intel wanted to move, they can't go it alone - they need the whole industry to shift at once.patrickjp93 - Sunday, February 22, 2015 - link

Graphene is nowhere near ready for CMOS processes. If it was IBM and Samsung would be gunning for it right this very moment. No one knows how to mass produce and interpose it the way you are insinuating, especially not to the high degree of purity required.DanNeely - Monday, February 23, 2015 - link

IBM sold it's foundry division to Global Foundries a few weeks ago. AFAIK the saile included the R&D portion of that business as wellKhenglish - Monday, February 23, 2015 - link

Intel is heavily researching 3-5 semiconductors. Their job offers are targetting engineers with 3-5 research experience. Going 3-5 would require HUGE fabrication changes, and 3-5 materials cost much more than Si which makes this path look dim, or at least very distant to me. 3-5 is also no magic solution. You go higher band-gap and get lower leakage and lower performance, or lower band gap with higher performance and higher leakage. There is no way to get more performance and lower leakage.Where have you seen graphene mass produced? Last I heard a square cm cost over $1M to manufacture, let alone actually successfully doping it. Remember that graphene must be a sheet of single atoms. Just having a single extra or missing atom has serious ramifications on device operation.

So it's not so simple, "WTF IS INTEL THINKING THEY NO NOTHING THEY ARE JUST MILKING US", finding something better than CMOS in Silicon while costing similar amounts is not trivial.

AbelDD - Thursday, February 26, 2015 - link

So then what on your guys thoughts on POET Technologies?"POET has been developed to include novel function architectures utilizing gallium arsenide

GaAs wafers, which enable the production of ICs that can be manufactured with processing speeds substantially in excess of those

currently obtained by ICs fabricated utilizing silicon wafers and complementary metal oxide semiconductor (“CMOS”) technology.

In addition, the POET technology incorporates positive and negative heterostructure field effect transistors (“HFETs”) as well as

positive and negative heterojunction bipolar transistors (“HBTs on a single GaAs wafer, thus substantially broadening the capabilities

of GaAs device technology,”), allowing for much improved power efficiency and speed, in addition to the combination of analog and

digital circuits in a single chip design.

A further innovation of POET would enable the design and implementation of optical and electronic devices within a single chip.

Using various device combinations the simultaneous fabrication of electronic and optical circuitry on a single integrated circuit device

is possible, an achievement that has not been accomplished using the silicon-based technologies currently dominating the market.

Anticipated key benefits of this optoelectronic integration capability include: (i) faster circuit/device speeds; (ii) lower device output

power; (iii) decreased cooling requirements; (iv) greater reliability; and (v) total system cost reductions. With POET’s materials

system based upon comprising direct bandgap III-V compounds, the active optical elements and high-performance electronic elements

can achieve a device density similar to that of silicon, the market’s traditional integrated circuit material.

The POET platform is relatively easy to implement utilizing industry standard tools and infrastructure. Utilizing industry standard

circuit design tools and process flows enables low adoption cost for implementation of POET. The POET wafer fabrication process is

similar to that of current industry standard silicon CMOS. POET manufacturing supports testing infrastructures, test-on-wafer

techniques, and post-fabrication procedures comparable to existing silicon CMOS procedures. The primary additional requirement to

convert silicon CMOS foundries to POET manufacturing would involve the acquisition of molecular beam epitaxy (“MBE”)

capability for the pre-processed GaAs wafers, or outsourcing the purchase of such wafers.

POET is differentiated from competing semiconductor processes such as silicon, silicon germanium or indium phosphide by its more

comprehensive set of functional capabilities and its ability to integrate them. Unlike existing processes which require the use of

multiple chips, circuit boards or sub-systems being linked together by either physical snap connections or multiple cable connections

that (i) produce the potential for multiple points of failure, (ii) require more space, increasing the physical end product size and (iii)

require greater power levels with the consequent production of excess heat, thus demanding additional space for cooling and

ventilation, we anticipate that POET will enable lasers, modulators, photoreceivers and passive optics as well as high-speed, lowpower

electronics on one monolithically-fabricated die. This would allow POET ICs, when fully developed, to demonstrate a lower

cost structure, increased power savings and increased reliability. "