The Samsung Galaxy S20+, S20 Ultra Exynos & Snapdragon Review: Megalomania Devices

by Andrei Frumusanu on April 3, 2020 9:30 AM ESTMemory Subsystems Compared

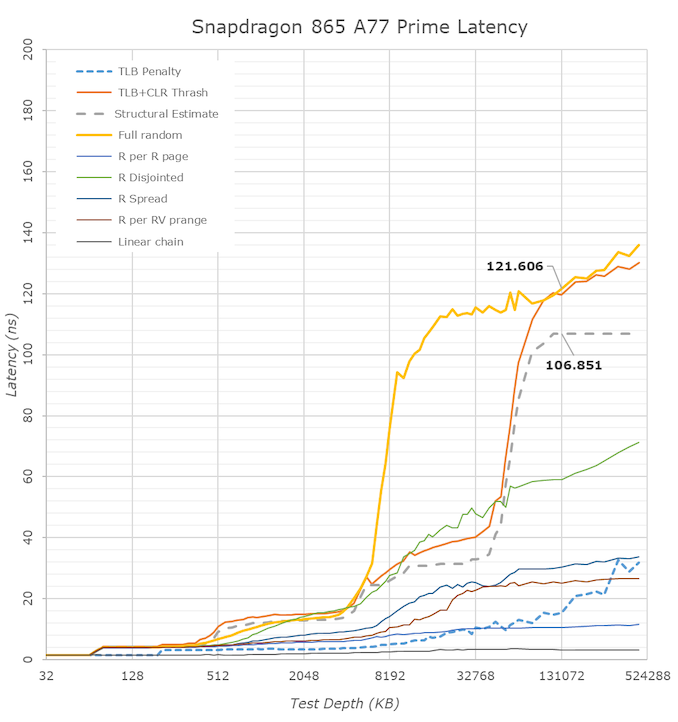

On the memory subsystem side, there’s quite a few big changes for both the Snapdragon 865 as well as the Exynos 990, as these are the first commercial SoCs on the market using LPDDR5. Qualcomm especially is said to have made huge progress in its memory subsystem, and we’re now able to verify the initially promissing results we saw on the QRD865 back in December with a production device.

And indeed, the news keeps on getting better for Qualcomm, as the new Galaxy S20 showcases even better memory results than we had measured on the reference device. The improvements over the Snapdragon 855 are just enormous and Qualcomm not only manages to catch up but very much now is able to beat the Exynos chips in terms of memory subsystem performance.

Arm very famously quotes that an improvement of 5ns in memory latency corresponds to an increase of around 1% in performance. And if that’s the case, Qualcomm will have had a ~12% improvement in CPU performance just by virtue of the new memory controller and SoC memory subsystem design. Our structural estimate in the memory latency falls in around 106 vs 124ns – most of the improvement seems to be due to how Qualcomm is now handling accesses to the DRAM chips themselves, previously attributing the bad latencies on the Snapdragon 855 due to power management mechanisms.

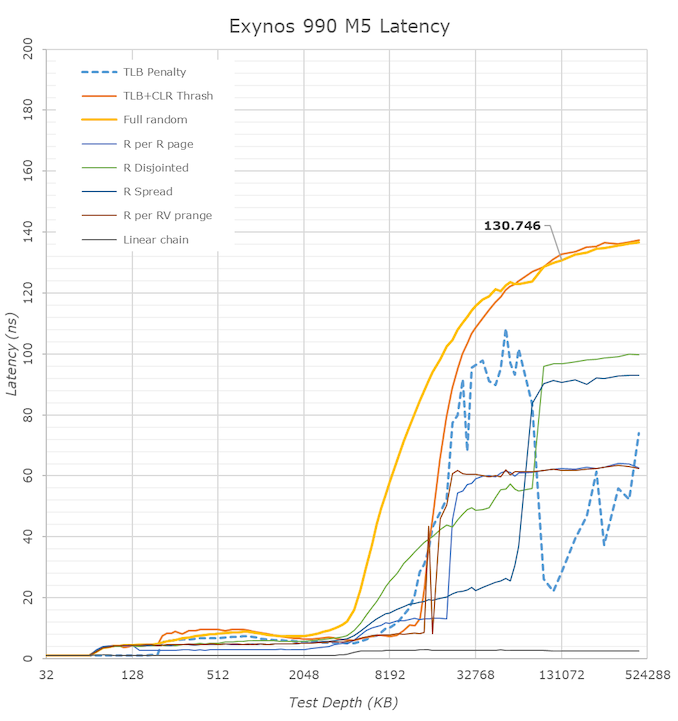

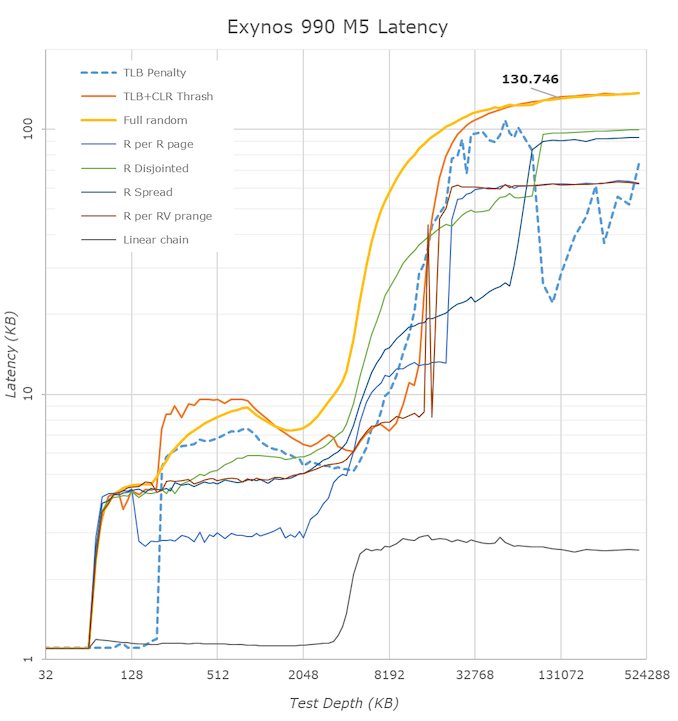

Samsung’s Exynos 990 also improves in memory latency compared to the Exynos 9820, but by a smaller margin than what the Snapdragon 865 was able to achieve. All latency patterns here are still clearly worse than the Qualcomm chip, and there’s some oddities in the results. Let’s zoom in into a logarithmic graph:

Comparing the Exynos 990 results vs the Exynos 9820, it’s now quite visible that the L2 cache has increased dramatically in size, similar to what we’ve described on the previous page, corresponding to the doubling of the available cache to a core from 1MB to 2MB. Samsung’s cores still have some advantages, for example they’re still on a 3-cycle L1 latency design whereas the Arm cores make due with 4-cycle accesses, however in other regards, the design just falls apart.

The TLB issues that we had described last year in the M4 are still very much present in the M5 core, which results in some absurd results such as random accesses over a 2MB region being actually faster than at 1MB. Cache-line accesses with TLB miss penalties now actually have lower access latencies in the L3 than in the L2 regions, and I have no idea what’s happening in the 16-64MB region in that test as it behaves worse than the 9820.

Examining the A76 cores of the Exynos 990, we see a much cleaner set of results more akin to what you’d expect to see from a CPU. Here we also see the 2MB SLC cache hierarchy in the 1-3MB region, meaning the Arm core cluster does have access to this cache, with the M5 cores bypassing it for better latency. Last year I had noted that the A76’s prefetchers had seen some massive improvements, and this is again evident here in the result sets of the two CPUs on the same chip as the middle cores actually handle some access patterns better than the M5 cores.

Samsung has had large issues with its memory subsystem ever since the M3 design, and unfortunately it seems they never addressed them, even with the more recent M5 core.

The Snapdragon 865 here is quite straightforward. The biggest difference to the 855, besides the improved DRAM latency, is the doubling of the L3 from 2 to 4MB which is also immediately visible. It still pales in comparison to the Apple A13’s cache hierarchy, but we do hope that the Arm vendors will be able to catch up in the next few years.

137 Comments

View All Comments

airdrifting - Monday, April 6, 2020 - link

I am actually a very forgiving person, I gave them 4 chances but they botched all. And then there was the Samsung Note catching fire left and right while Samsung PR was lying to cover up, that was the last straw for me. I was very skeptical when I switched to Oneplus, but I was very impressed with the build quality and speedy updates, the only weak point was the camera.tuxRoller - Sunday, April 5, 2020 - link

Any thoughts as to why Huawei was having issues with the A77?BedfordTim - Sunday, April 5, 2020 - link

They say the battery life penalty means the extra performance isn't worth it. This fits with their energy use figures in the benchmarks which are very good. It also makes sense from a user perspective as the extra performance will not be noticeable in everyday use.iphonebestgamephone - Monday, April 6, 2020 - link

How come qualcomm improved efficiency then? Its more like hisilicon had no time.Andrei Frumusanu - Monday, April 6, 2020 - link

I don't think they had issue, they probably didn't have time.tuxRoller - Tuesday, April 7, 2020 - link

You're probably right.Any idea as to why they were running late this time? The arm update cadence has been reliably in May since at least the A72.

** A - R ** - Sunday, April 5, 2020 - link

Andrei,For storage benchmarks, how about this (cpdt) app ?

https://play.google.com/store/apps/details?id=com....

Andrei Frumusanu - Monday, April 6, 2020 - link

It's not useful - there's very different aspects of storage performance on Android that's not covered by these traditional tests.Arian_amg - Sunday, April 5, 2020 - link

Thanks for great reviews:)I waited for this one like hell... With these Corona situations it's hard to find entertaining content and as always you nailed it best chipset reviews I've ever seen most will getaway with some benchmark and thats it

Im really looking forward for the dimensity 1000 and kirin 820 to get a proper understanding of new Valhalla cores with a proper node

(btw do you agree with huawei that they said they didn't use a77 because it didn't reach a certain clock(I know it had much higher ipc than a76)?)

Andrei Frumusanu - Monday, April 6, 2020 - link

HiSilicon probably had less time to integrate the A77 and thus didn't reach good clocks.