AMD Ryzen 9 5980HS Cezanne Review: Ryzen 5000 Mobile Tested

by Dr. Ian Cutress on January 26, 2021 9:00 AM EST- Posted in

- CPUs

- AMD

- Vega

- Ryzen

- Zen 3

- Renoir

- Notebook

- Ryzen 9 5980HS

- Ryzen 5000 Mobile

- Cezanne

CPU Tests: Microbenchmarks

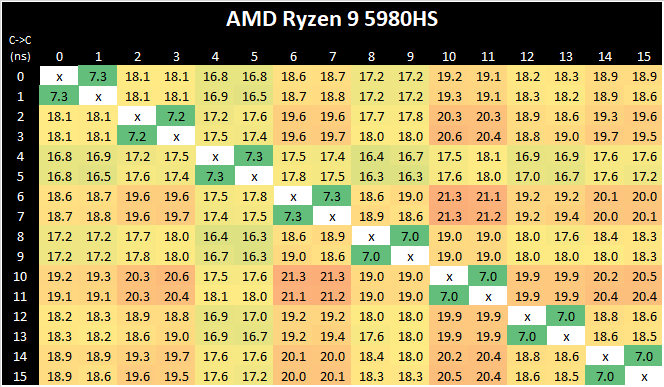

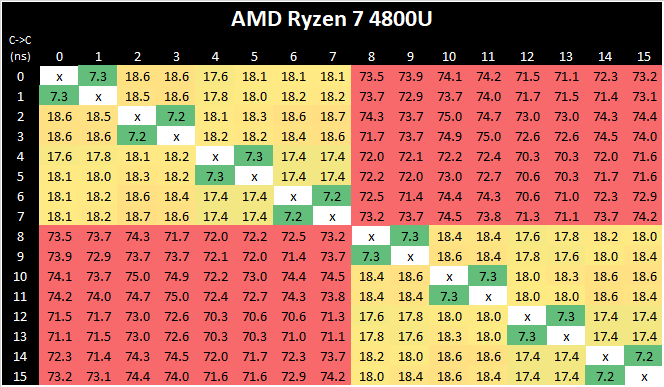

Core-to-Core Latency

As the core count of modern CPUs is growing, we are reaching a time when the time to access each core from a different core is no longer a constant. Even before the advent of heterogeneous SoC designs, processors built on large rings or meshes can have different latencies to access the nearest core compared to the furthest core. This rings true especially in multi-socket server environments.

But modern CPUs, even desktop and consumer CPUs, can have variable access latency to get to another core. For example, in the first generation Threadripper CPUs, we had four chips on the package, each with 8 threads, and each with a different core-to-core latency depending on if it was on-die or off-die. This gets more complex with products like Lakefield, which has two different communication buses depending on which core is talking to which.

If you are a regular reader of AnandTech’s CPU reviews, you will recognize our Core-to-Core latency test. It’s a great way to show exactly how groups of cores are laid out on the silicon. This is a custom in-house test built by Andrei, and we know there are competing tests out there, but we feel ours is the most accurate to how quick an access between two cores can happen.

AMD’s move from a dual 4-core CCX design to a single larger 8-core CCX is a key characteristic of the new Zen3 microarchitecture. Beyond aggregating the separate L3’s together for a large single pool in single-threaded scenarios, the new Cezanne-based mobile SoCs also completely do away with core-to-core communications across the SoC’s infinity fabric, as all the cores in the system are simply housed within the one shared L3.

What’s interesting to see here is also that the new monolithic latencies aren’t quite as flat as in the previous design, with core-pair latencies varying from 16.8ns to 21.3ns – probably due to the much larger L3 this generation and more wire latency to cross the CCX, as well as different boost frequencies between the cores. There has been talk as to the exact nature of the L3 slices, whether they are connected in a ring or in an all-to-all scenario. AMD says it is an 'effective' all-to-all, although the exact topology isn't quite. We have some form of mesh with links, beyond a simple ring, but not a complete all-to-all design. This will get more complex should AMD make these designs larger.

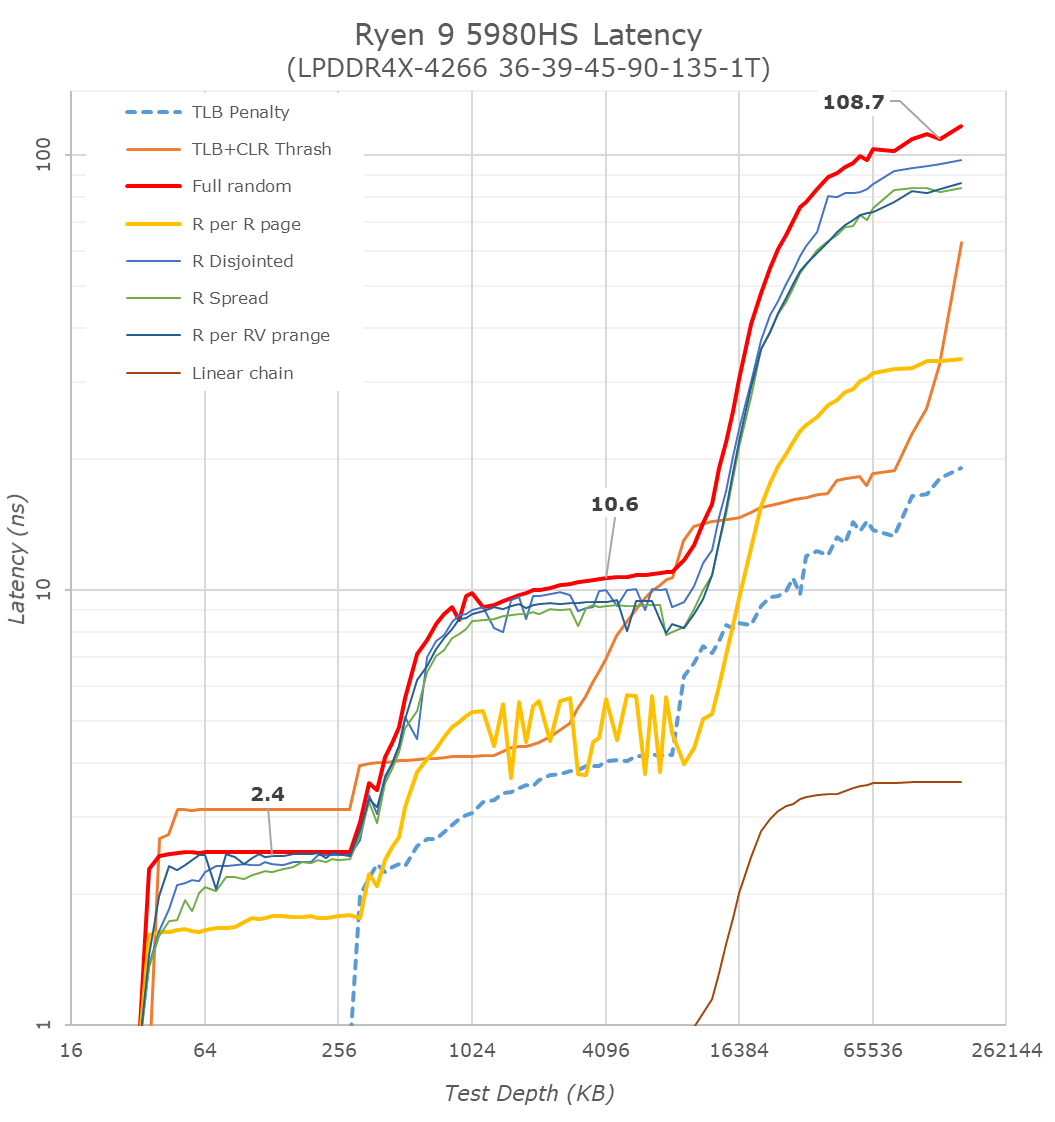

Cache-to-DRAM Latency

This is another in-house test built by Andrei, which showcases the access latency at all the points in the cache hierarchy for a single core. We start at 2 KiB, and probe the latency all the way through to 256 MB, which for most CPUs sits inside the DRAM (before you start saying 64-core TR has 256 MB of L3, it’s only 16 MB per core, so at 20 MB you are in DRAM).

Part of this test helps us understand the range of latencies for accessing a given level of cache, but also the transition between the cache levels gives insight into how different parts of the cache microarchitecture work, such as TLBs. As CPU microarchitects look at interesting and novel ways to design caches upon caches inside caches, this basic test proves to be very valuable.

As with the Ryzen 5000 Zen3 desktop parts, we’re seeing extremely large changes in the memory latency behaviour of the new Cezanne chip, with AMD changing almost everything about how the core works in its caches.

At the L1 and L2 regions, AMD has kept the cache sizes the same at respectively 32KB and 512KB, however depending on memory access pattern things are very different for the resulting latencies as the engineers are employing more aggressive adjacent cache line prefetchers as well as employing a brand-new cache line replacement policy.

In the L3 region from 512KB to 16 MB - well, the fact that we’re seeing this cache hierarchy quadrupled from the view of a single core is a major benefit of cache hit rates and will greatly benefit single-threaded performance. The actual latency in terms of clock cycles has gone up given the much larger cache structure, and AMD has also tweaked and changes the dynamic behaviour of the prefetchers in this region.

In the DRAM side of things, the most visible change is again this much more gradual latency curve, also a result of Zen3’s newer cache line replacement policy. All the systems tested here feature LPDDR4X-4266 memory, and although the new Cezanne platform has a slight advantage with the timings, it ends up around 13ns lower latency at the same 128MB test depth point into DRAM, beating the Renoir system and tying with Intel’s Tiger Lake system.

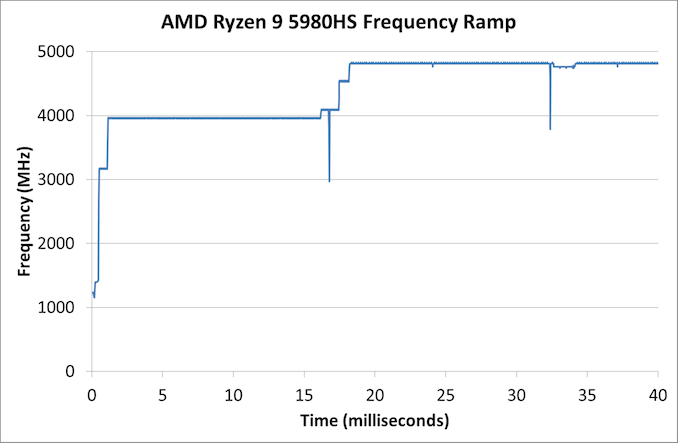

Frequency Ramping

Both AMD and Intel over the past few years have introduced features to their processors that speed up the time from when a CPU moves from idle into a high powered state. The effect of this means that users can get peak performance quicker, but the biggest knock-on effect for this is with battery life in mobile devices, especially if a system can turbo up quick and turbo down quick, ensuring that it stays in the lowest and most efficient power state for as long as possible.

Intel’s technology is called SpeedShift, although SpeedShift was not enabled until Skylake.

One of the issues though with this technology is that sometimes the adjustments in frequency can be so fast, software cannot detect them. If the frequency is changing on the order of microseconds, but your software is only probing frequency in milliseconds (or seconds), then quick changes will be missed. Not only that, as an observer probing the frequency, you could be affecting the actual turbo performance. When the CPU is changing frequency, it essentially has to pause all compute while it aligns the frequency rate of the whole core.

We wrote an extensive review analysis piece on this, called ‘Reaching for Turbo: Aligning Perception with AMD’s Frequency Metrics’, due to an issue where users were not observing the peak turbo speeds for AMD’s processors.

We got around the issue by making the frequency probing the workload causing the turbo. The software is able to detect frequency adjustments on a microsecond scale, so we can see how well a system can get to those boost frequencies. Our Frequency Ramp tool has already been in use in a number of reviews.

Our frequency ramp showcases that AMD does indeed ramp up from idle to a high speed within 2 milliseconds as per CPPC2. It does take another frame at 60 Hz (16 ms) to go up to the full turbo of the processor mind.

218 Comments

View All Comments

Spunjji - Monday, February 1, 2021 - link

I'm aware of all of the above, but it still doesn't justify the original claims being made - and "Potentially also on the menu would be a faster peak clock rate" is nothing but speculation. Based on what we know about the design and the relatively poor clock scaling in respect of TDP shown between the A14 and M1, I'd say it's extremely unlikely that Apple will be able to push clocks up by more than a couple of hundred megahertz without a significant redesign.What Apple will most likely have in that TDP range is something that's performance-competitive with Cezanne on the CPU side in native applications, significantly outclasses it on the GPU side, and maintains a perf/watt advantage commensurate with the node advantage that largely disappears when running translated code.

It's still far better than what Intel have, but it's not going to redefine the industry. If that order of advantage were enough to do so, then AMD wouldn't have existed after 2007.

GeoffreyA - Sunday, January 31, 2021 - link

"Apple will outclass everything x86 once they introduce their second gen silicon"I've noticed the idea circulating is that the M1 is Apple's first-generation CPU. Sure, it may be the first one going into a computer, but as far as I'm aware, the M1 descends from the A14, which goes back to the A6 of 2012. How many iterations is that? Nine? Granted, some might be "ticks," but this certainly isn't a brand-new design. Zen 3, despite borrowing from Athlon, Bulldozer, and Core, is on its 3rd iteration, or 4th if one counts Zen+.

Lucky Stripes 99 - Tuesday, January 26, 2021 - link

Not only have iGPUs cannibalized the sub-$100 discrete GPU market, but they have also chewed into the cool and quiet GPU market. If you have a HTPC or compact mITX system, your options aren't that great. I'd really like a GTX 3060L on a low profile PCIe card, but I won't hold my breath.Also, I love the return of the 16:10 screen format. I'd kill for a 27" desktop version of the X13's screen with the same resolution and color coverage.

DigitalFreak - Tuesday, January 26, 2021 - link

What's the problem with integrated graphics in a HTPC?Lucky Stripes 99 - Tuesday, January 26, 2021 - link

New features tend to come slower to iGPU parts than to discrete GPU parts. As example, it used to be very difficult to build a 4K60p system with a Raven Ridge APU because so few boards supported HDMI 2.0. Likewise, you're often stuck with an older video decoder/encoder than what is available on the discrete GPU market. Luckily the only feature missing from the latest generation of AMD parts is hardware AV1 decoding which will come with the RDNA2 APUs next round.dudedud - Tuesday, January 26, 2021 - link

I thought you will be including the M1 in more benchmarks besides GB and SPEC.:/

danwat1234 - Tuesday, January 26, 2021 - link

"But what is perhaps worrying is the temperature, being reported as a sustained 92-94ºC on average. That’s quite high. " --> 94C is fine, the silicon is rated to handle it 24/7. What is strange to me is that it most of the tests, the CPU temperature stays in the 80s, when there is more thermal headroom to go. It could clock higher.Fulljack - Wednesday, January 27, 2021 - link

80°C means either you have a glaring jet sound on your laptop fans or downclock it enough to keep it quite.Deicidium369 - Wednesday, January 27, 2021 - link

quite what?and pretty sure glaring refers to vision, while blaring refers to SPL

abufrejoval - Tuesday, January 26, 2021 - link

I wonder why you peg the mobile 8-core against a desktop 6-core instead of the 5800X...?Having the various 8-cores side-by-side allows a much better understanding of how architecture and power settings compare generally.

BTW tried do the manual comparison via Bench, but it seems the Chezanne results aren't in there yet.